telos systems

#### TABLE OF CONTENTS:

Introduction

A Note about Telos Systems and Service

Operation

Record operation Playback Auto Answer/Play mode

Selecting number of plays in auto answer mode

About the Battery and the Battery Switch

Installation

General Remote Control Remote Control Example Schematic

Circuit Description & Troubleshooting

Introduction

Built-in Diagnostics

Board Removal

Circuit Discussion - Digital Section

Circuit Discussion - Audio Section

#### **Appendix**

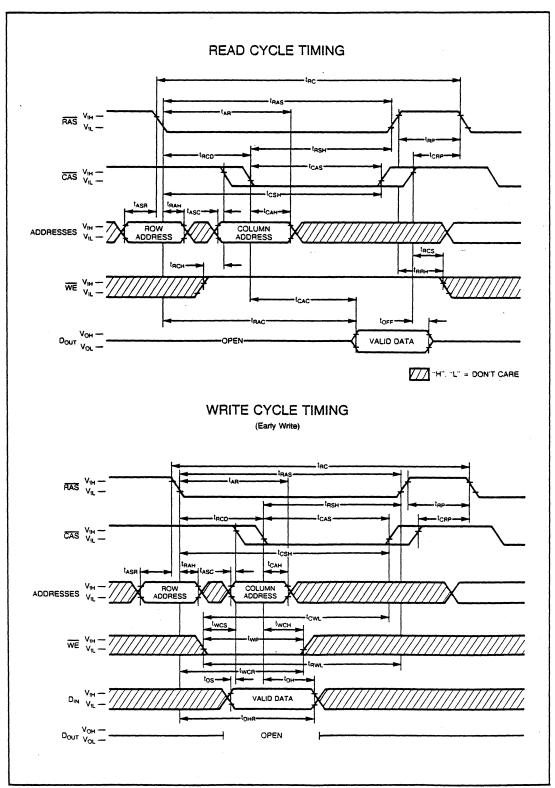

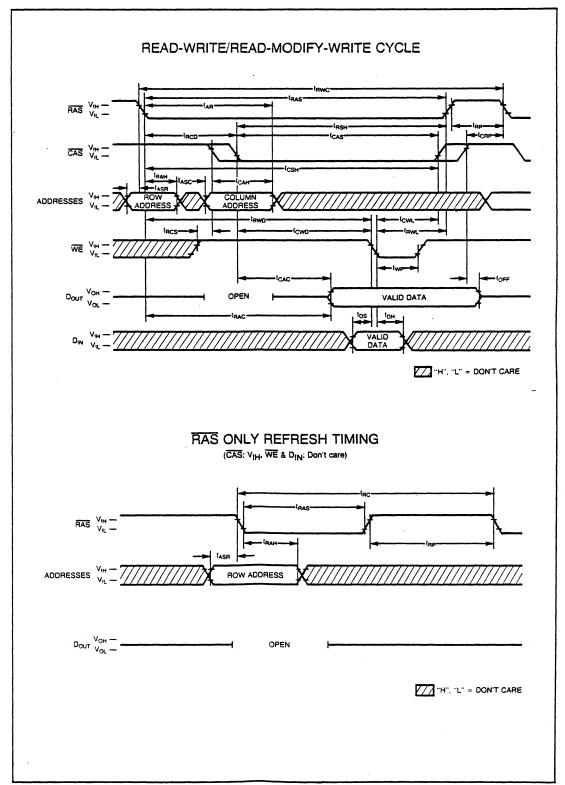

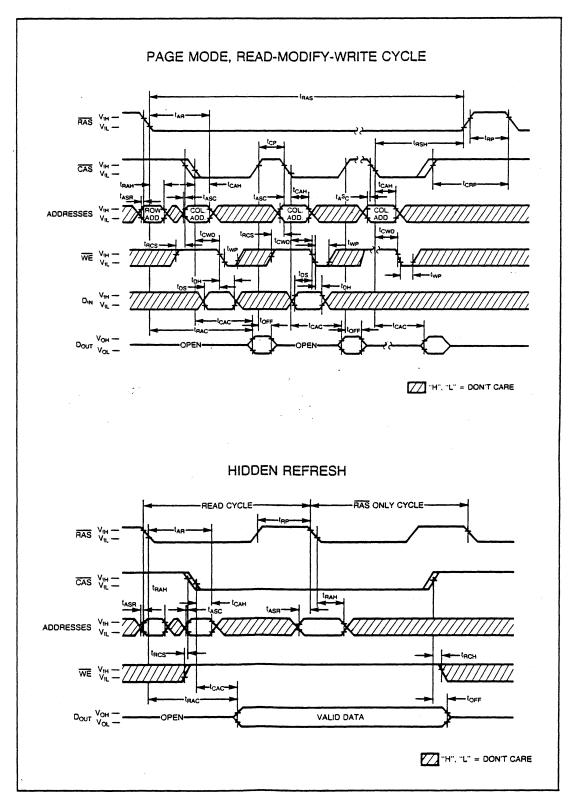

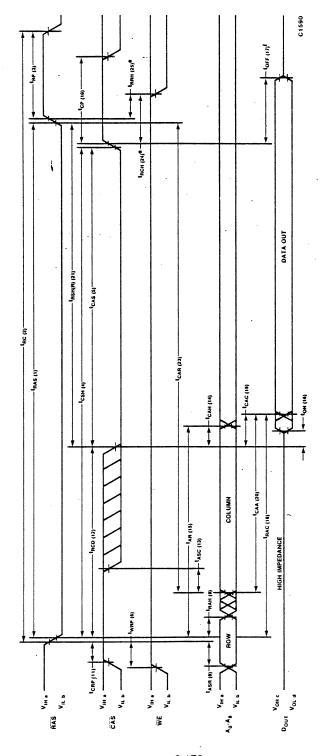

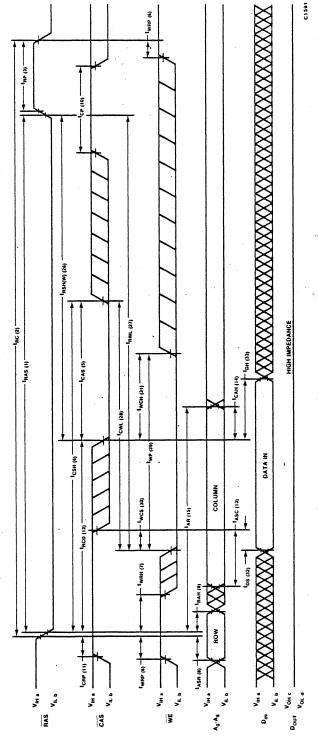

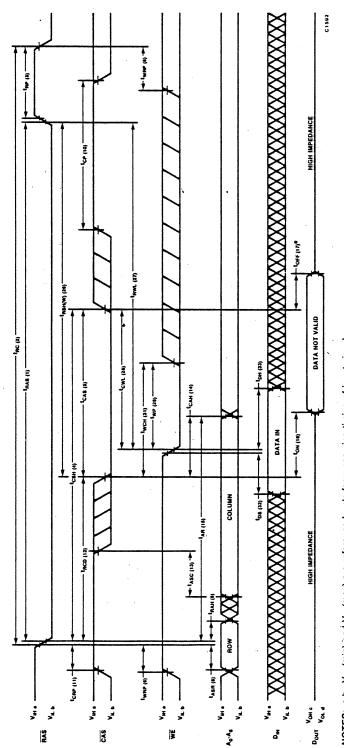

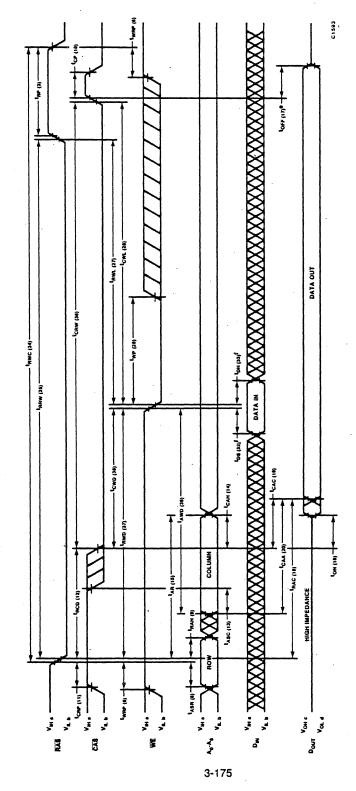

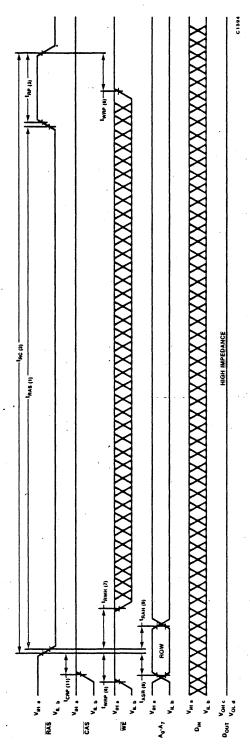

**Timing Charts**

Manufacturers Data Sheets

Warranty

#### Introduction

The Echo is the second product from a very small company, Telos Systems. As with the Telos 10 digital hybrid system, the Echo was designed to solve a problem which I have encountered in my own work as a radio station engineer.

Unhappily, I had been using cart machines for an application for which they are ill-suited: playing recorded messages to listeners on the phone. Cartridges are OK for on-air playback, but are frequently unreliable (to say the least!) when they are called upon to serve the continuous playback demands of concert lines, weather lines, ski information lines and the like.

At my station, our concert line gets as many as 1,000 calls a day! The has-been cart machines we were using were a constant source of frustration. Broken tapes, worn heads and bad pinch rollers often resulted in listener complaints, angry program directors, and unhappy engineers.

Technology to the rescue!

Recent advances in digital speech companding technology, combined with rapidly falling RAM memory cost has made possible a nifty solution to the problem of answering the phone reliably: record and play the message from solid-state memory IC's, not from unreliable mechanical contraptions.

The Echo uses 1 Mbyte of dynamic ram memory controlled by a Z80 processor. A special signal processing IC allows 4 minutes of telephone-grade speech to be stored.

A built-in phone line answering circuit allows simple no-hassle installation: merely provide AC power, and connect the phone line.

Operation is simple too. The control layout is designed to simulate a simple cassette machine. Functions are labeled so that anyone familiar with analog tape machines can intuitively figure-out what to do without resorting to a manual or learning complicated control sequences.

# Introduction (cont)

In addition there are a few neat features to wow jaded GM's and PD's. An LED display counts seconds in the record mode and number of calls received in the auto-answer/play mode. A front panel speaker makes checking messages easy. Full remote control facilities allow messages to be recorded in the production studio.

There are a few features engineers will like, too. A front panel XLR-type balanced mike input, along with a balanced line-level input on the rear panel. A battery back-up scheme and a special circuit called a "watchdog timer" that prevents problems from power glitches and failures. An effective AGC to prevent record level problems. Solid, conservative design and construction. Built-in diagnostics. Complete component-level troubleshooting information, or a board-swap repair program your choice. A quality PC board with all component legends screened clearly. Easy access to all parts.

The goal of Telos Systems is to provide high-quality, creative and cost-effective solutions to broadcast problems. And, of course, a few bucks to the owner, ME! So far, so good.

As always, keep on keepin' the GM happy...

- Steve Church

# A note about Service

Telos Systems is a small company. I'm committed to provide the advantages of small company service to you.

A very few service-oriented dealers have been enlisted to be your front-line contact in the event you should need questions answered or help of any kind. This allows me to continue in my primary role as a working-stiff CE, while at the same time ensuring that you get what you need when you need it.

Echo dealers have been instructed, however, to have you contact me directly in the event that they are unable to solve your problem quickly.

This strategy has been successful with Telos 10 owners. In almost every case where a part or a board-swap was required in order to solve a problem, the part or board was shipped within one day. It is my goal to have no defects, of course - but if you have an Echo malfunction, you can count on a quick solution.

#### Operation

The Echo was designed to be easily understood and operated by anybody who knows how to use a simple cassette recorder. Use of the Echo should be intuitive, for the most part. However, there are a few interesting features/quirks that may not be immediately apparent.

Since you've got to record before you play, let's discuss that first.

RECORDING - In order to record, you'll have to connect either a microphone to the front panel XLR input or a line—level source to the rear-panel phone jack. See the installation section for details.

Adjust the record level control so that the led level display is indicating normally. This is not critical since the internal automatic gain control will take care of all but the most extreme input levels.

Press the RECORD button and talk. The SECONDS/COUNTER display will indicate elapsed time. The maximum time is *256* seconds.

When you've finished your message, press the STOP button. This terminates recording and causes an ending "marker" to be placed at the end of your message. During recording, you may pause by pressing the PAUSE button. You are then able to resume recording by pressing the RECORD button again.

PLAYING back - Press the PLAY button and adjust the speaker level control for the desired volume.

You can use the PAUSE button in the play mode just as you would expect. In fact, one potentially useful feature is that you can go into the record mode after pausing during playback. This allows you to extend an already recorded message or to change an existing "tag."

AUTO ANSWER/PLAY mode -This is the mode which is used to answer incoming phone calls. To establish the auto answer mode, press the white AUTO ANSWER button. As calls come in, they are answered by the ECHO and the LED counter counts the number of calls (up to 9999, then starts over again at 0000). The bar graph indicates the presence of audio.

Loss of AC power can result in a meaningless call-count display. Pressing the stop button will reset the counter to zero.

If the PLAY button is pressed when in the auto answer mode, the message will be played-back continuously. Since the Echo is likely to be used for long periods of time without attention in the auto answer mode, it incorporates a special feature called a "watchdog timer" to ensure that power line failures and "glitches" don't cause the unit to malfunction.

If there is a power failure, the battery will maintain the message in memory for approximately one hour. When power is restored, the Echo will automatically go into the auto answer mode.

Power line glitches can also cause the unit to go into the auto answer mode. No loss of memory will occur.

If erratic operation is observed, a manual reset may be required. This is accomplished by pressing the AUTO button.

Selecting number of plays in the Auto Answer mode

The number of times the message is played to callers is selectable using an internal "dip switch."

The unit is shipped with the switch set for single play operation. If you need to select two or three plays, you will need to remove the top cover to get access to the dip switch.

With the cover removed, locate the dip switch, and turn on only the switch corresponding to the number of plays you desire.

This dip switch is also used to access internal test diagnostics described later.

CAUTION: With the top removed, there is 110V AC present near the left rear of the unit (by the fuse and power connector, and also the white plug that mates with J2). If you are unsure of where the AC is present, PULL THE PLUG BEFORE YOU MUCK ABOUT WITH THE INTERNALS OF THE ECHO!

#### About the Battery and the Battery Switch

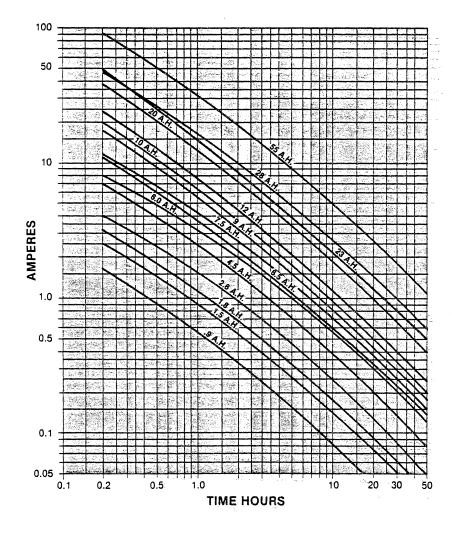

The Gel-Cell-type battery used in the Echo may have to be replaced after three to four years of service, according to the manufacturer.

It's probably a good idea to check the battery every now and again by pulling the AC cord to see how long the message is retained in memory.

The rear panel battery switch is provided to keep the battery from being fully discharged when the unit is expected to be unplugged for a long period of time (over an hour). When you expect to have it unplugged, turn the battery switch to the off position.

The Echo is shipped with the battery charged and the switch off.

#### Installation

Echo installation is very simple.

- 1) Apply AC.

- 2) Turn the battery switch (on the rear panel) to the on position. If the battery has been allowed to fully discharge, it may be a few moments for all of the Echo functions to become operational. In addition, if memory contents have been lost because of battery discharge, pressing the play button will yield a solid tone at very high level. Doing this while drinking coffee is not recommended.

- 3) Plug the phone line into the modular phone connector on the rear panel.

- 4) Plug a microphone into the front panel XLR connector, or a line level input into the rear panel 1/4" phone jack.

The rear panel line input is balanced and uses a tip-ring--sleeve "stereo" type 1/4" jack.

For balanced sources, the two hot leads go to tip and ring and the shield goes to the sleeve.

For unbalanced sources, use a "mono-type" plug, or short the sleeve to the ring of a tip-ring-sleeve type plug. The hot audio lead would then go to the tip, of course, while the shield would go to the sleeve.

If you need to use any of the remote control functions, move ahead to the next page.

#### Remote Control

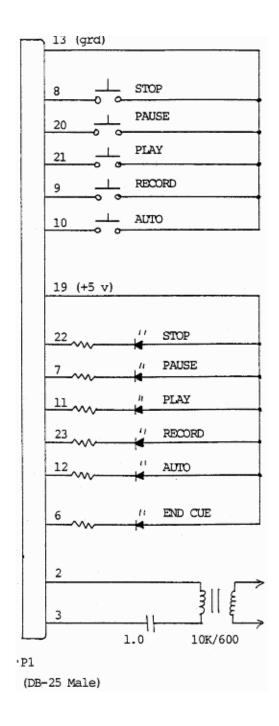

The front panel switches and the indicator LEDS are remotable via the rear panel DB25 25-pin connector. A balanced audio output is also available on this connector.

As described earlier, a separate 1/4" phone jack is provided for line level input. The mic and line inputs are simultaneously active.

The audio output level is approximately -10 dBm.

The remote inputs connect between the ground pin and the appropriate input function pins. They are thus pulling a high voltage (5v) to ground. The internal pull-up resistor is 1K. The inputs are well buffered and debounced, so there should be no problem with long cable runs.

The outputs are pulled to ground when active. Thus your external indicators should connect between the +5v pin and the appropriate output pin. YOU MUST PROVIDE THE REQUIRED CURRENT-LIMITING RESISTORS IF YOU USE LEDS AS YOUR REMOTE INDICATORS. Usually, 330 ohms is the value used (for 15 ma LED current).

| Remote Connector Pin-out: |                                                                                                               | Pin                           |                     |

|---------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|

|                           | Function STOP switch PAUSE switch PLAY switch RECORD switch AUTO switch Ground (switch common) STOP indicator | 8<br>20<br>21<br>9<br>10<br>1 |                     |

|                           | PAUSE indicator PLAY indicator RECORD indicator AUTO indicator +5v (indicator common)                         | 7<br>11<br>23<br>12<br>2      |                     |

|                           | Audio out +<br>Audio out -                                                                                    | (see ne                       | xt page)            |

|                           | Phone line<br>Phone line                                                                                      | 24<br>25                      |                     |

|                           | End Cue output                                                                                                | 6                             | (closure to ground) |

#### Remote Control Example Schematic

#### Note:

Audio output at pins 2 & 3 are transformer balanced. When the Echo is answering a call, this output is connected to the phone line. The capacitor and transformer indicated are required to isolate user equipment if it is expected that a call might be answered while this output is connected.

#### Circuit Description & Troubleshooting Introduction

The Echo circuitry is made up of analog and digital sections. The analog audio processing and output sections should present no problem to the experienced troubleshooter. Finding problems should be as simple as tracing with an oscilloscope to find where in the circuit the signal guits or becomes distorted or whatever.

The digital section has as it's central element the very common Z80 microprocessor. While a "textbook simple" approach has been taken toward the design of this portion of the Echo, some tricky troubleshooting may be required to nail down problems, particularly if the timing circuits or dynamic ram interface section is involved.

If you are unfamiliar with microprocessors, and wish to learn, a good tutorial discussion of Z80-based circuits is given in BUILD YOUR OWN Z80 COMPUTER, Steve Ciarcia, Byte Books. This book is often found at local bookstores, or may be ordered by them.

Diagnostic routines are included to help you find certain kinds of problems. Since these are very simple to use, they are always a good first step. The next manual section describes the use of these routines.

While full component-level troubleshooting information is included here, keep in mind that a board swap repair program is available on all Telos products, if you prefer not to tackle nitty-gritty troubleshooting yourself. Please contact your dealer for particulars.

#### Circuit Description and Troubleshooting Diagnostics

There are two diagnostic routines, which are normally used during production testing which may be useful if you suspect problems with the microprocessor or memory sections of the echo. One tests the basic functioning of the Z80 processor and the input/output circuits; the other is used to test the memory array and pinpoint bad memory chips.

#### THE I/O TEST DIAGNOSTIC MODE -

This diagnostic mode is used to confirm the proper operation of the core microprocessor circuit and the input/output sections.

The test is entered by turning dip switch #1s 2 and 3 ON with #1 off (open) and then causing a reset by pressing the AUTO button. The AUTO button led will illuminate. Each button will light it's associated led as long as it is pressed. The AUTO button will pull-in the line relay.

#### THE MEMORY TEST DIAGNOSTIC MODE -

This mode is entered by turning all 3 of the dip switches on (opposite "open") and then performing a reset by pressing the AUTO button.

The STOP LED will flash. To begin the test, press the STOP button. The counter will begin counting and the STOP LED will be on solid.

A successful completion of the test will result in the counter indicating 256, and the STOP led will flash again.

If there is a memory error, all of the LEDS will flash and the line relay will cycle. The counter indicates the bad memory column as follows:

| 0-63    | column0 (U2-9)   |

|---------|------------------|

| 64-127  | column1 (U10-17) |

| 128-191 | column2 (U18-25) |

| 192-255 | column3 (U26-33) |

|         |                  |

#### Diagnostics (cont)

Pressing the STOP button again will isolate the row position of the bad IC within the column previously indicated. A 0 count corresponds to the memory IC nearest the rear panel, while a 7 count would indicate that the IC nearest the front is bad.

When pressing the STOP button, hold it down long enough only to start the test process. Otherwise, some counts may be lost, and you may be misled as to the location of the faulty IC.

## Circuit Description and Troubleshooting Board removal

The main board is removed by:

- 1) Unscrewing the 1/4" phone jack retaining nut,

- 2) Unscrewing the 2 screws that hold the DB- 25 multi-pin remote connector to the rear panel,

- 3) Unscrewing the 3 retaining screws accessible from the top,

- 4) Unscrewing the 2 screws securing the spacers near the power transformer FROM THE BOTTOM OF THE CASE (the transformer obstructs access to the screws from the top). Of course, if you have a screwdriver with a small enough shaft, there is no reason you couldn't remove the screws from the top.

#### SPECIAL NOTE:

The power supply regulators must have a heat sink in order to operate properly. This means that you should have the two regulator mounting screws in place while the Echo is powered-up. No permanent damage will occur if you forget to do this, but there will be very flaky problems as the regulators heat-up and then shutdown as they are supposed to.

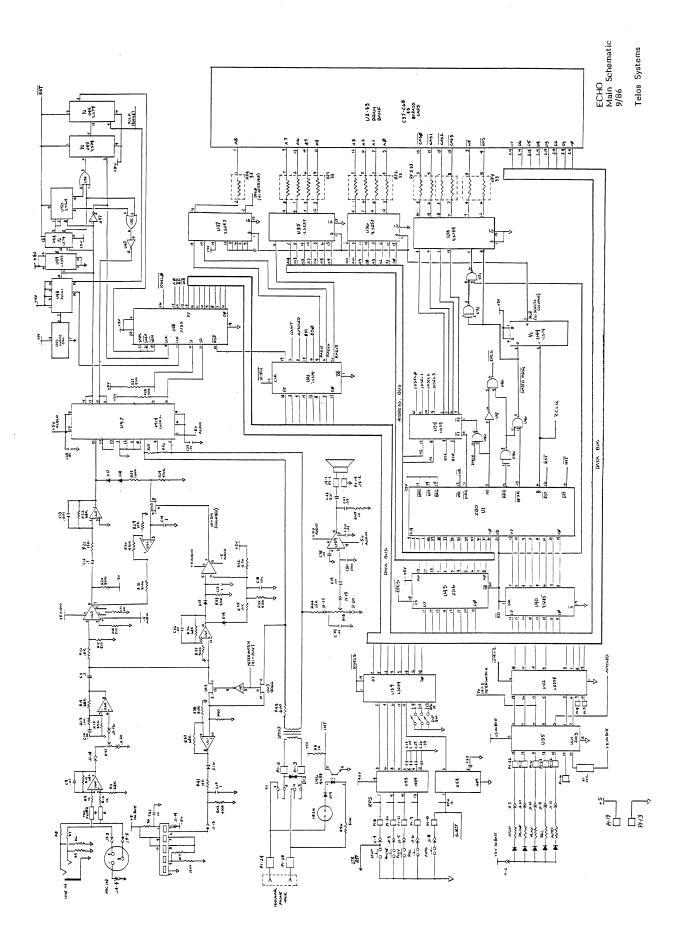

Circuit Description and Troubleshooting Circuit discussion - digital section

All digital signals are TTL compatible levels which means that a high signal would be 2.4v or above, and a low would be under .8v.

The central circuit element is the Z80 microprocessor. The Z80 moves the digitized audio from the signal processor to and from the appropriate memory locations and provides all of the control functions by responding to the pushbutton and other inputs. With the exception of the dynamic ram circuits, the approach used in the echo is "textbook simple."

The Z80 (U1) executes the machine-level software programmed into the 2716 EPROM (U43). U43 puts it's data on the bus when it's EPCS pin goes active. The EPROM is selected when address line A15 is low; that is when the Z80 is requesting data from locations hex 0000 to 7FFF. Sections of U46 and U47 provide the required gating to ensure the EPROM is selected only when A15 is low MRQ is active.

U40 is a buffer. It provides the required drive to the data bus from the Z80. It also buffers the Z80 input, as well. The Z80 RD output causes U40's direction of operation to be appropriate.

There is one input IO port, U39. It puts the input data on the bus when it's select line, IOSEL3 becomes active. U53 and U54 are special buffer ICs, which are intended for use with long input lines (they're actually intended for use with computer serial RS- 232 inputs); thus, they have provision for rejecting spurious inputs. The capacitors, C23-26 slow input response for this purpose.

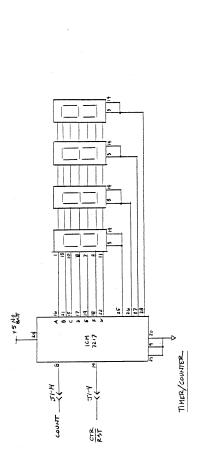

There are two output ports, U42 and U41. U42 is used to drive the indicator LEDS, the END CUE output, and the line relay. U41 is the bank select port for the memory section and drives the AUTO indicator and the front panel LED counter COUNT line. Both of these pick up and latch data from the bus when their IOSEL lines go active.

The IOSEL signals are generated by one section of U34, which decodes the lower two address lines to four outputs.

The signal processor, a special programmed NEC 7730 IC (U58), operates as a peripheral to the Z80. It is, in effect, both an input and an output port. This is where the Z80 sends the digitized audio data during play, and where it gets it during record.

U57 is a special type of Analog-to-Digital and Digital-to-Analog converter called a CODEC. Useful for telephone-grade audio, it contains built-in input and output filters. It connects directly to the signal processor via two serial lines, SI and SO.

The circuit elements in the upper right corner of the schematic are the clock generator. It generates synced clock outputs for the 7730, the Z80, and the CODEC. The 7730 gets 8 MHz, the Z80 gets 4 kHz, and the CODEC gets 2 kHz plus a special frame-sync signal. See the clock timing chart for output waveforms.

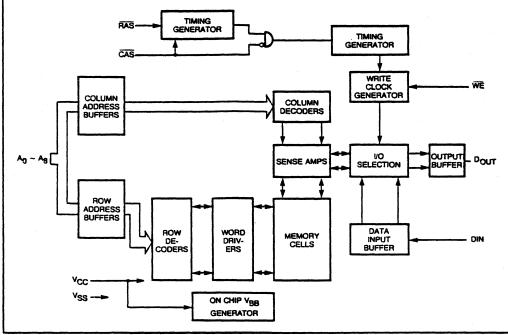

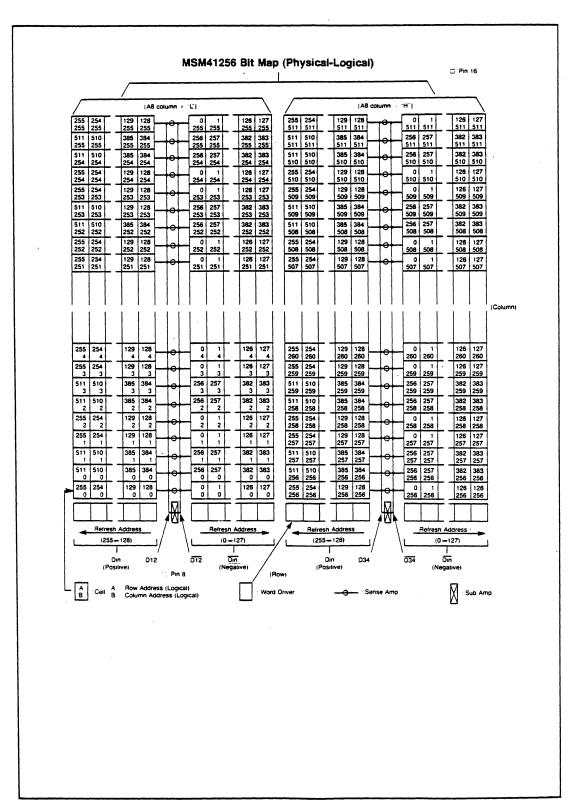

The most difficult part of the Echo to understand is the dynamic memory section. The Echo has 1 megabyte of memory. Each DRAM chip has a capacity of 256K bits. Each byte needs 8 chips, since each chip is only one bit "wide", to use the usual computer terminology. Thus, the memory bank consists of 4 rows of 8 chips to make up the 1 Meg by 8-bit memory array.

The 4 rows are accessed in order during the 4-minute play/record time, with the first row storing the first minute; the second row the second minute, etc.

Since the Z80 cannot directly address 1 Mbyte of memory, a bank select scheme is used to extend the system addressing range. When it's time to switch to the next bank, the new bank value is output to the U41 output port. We're using 15 address lines from the Z80 directly for the address Isb's (A0-A14), and 5 from the bank select port for 20 total address bits. This is the required number of bits to address 1 Mbyte. BS1 and BS2 are decoded by one-half of U34 to select from the 4 DRAM rows.

Dynamic memory is the lowest-cost and least space/energy consuming way to get lots of storage capacity. It is certainly the only practical way, at present, to get enough capacity cheaply for applications like the Echo.

There are disadvantages to using DRAM's which must be dealt with, however. Since DRAM's store information as a charge on a capacitor, the memory must remain powered and "refreshed" by the Z80 software regularly in order to retain data. The battery is used to ensure that power interruptions don't cause the message to be erased. A watchdog timer, discussed later, makes sure the Z80 is always running so that it can perform it's refresh function.

The second DRAM disadvantage is the complexity of the interface circuit. In order to keep the memory IC packages small, the number of pins are limited and the address inputs are "multiplexed." That is, the 18 required address inputs are shared on only 9 pins. Internal latches retain the 9 bit values in order that the full 18 bits are available at once to select the appropriate memory cell. Two inputs, RAS (Row Address Strobe) and CAS (Column Address Strobe) are used to latch in the appropriate address bits at the right time. The address multiplexing and the control of the CAS and RAS strobes are accomplished using a number of the remaining IC's.

There are few things in the known universe as terrifying as the timing requirements of DRAM's! Take a look at the timing diagram (in the appendix) for an idea of what's involved. Fortunately for you, the circuit is already designed - you just have to fix it. Remember, it did work once - so, it certainly can again!

First, let's examine what happens in the record mode. You will need to refer to the memory timing chart and the schematic in order to make sense of this discussion.

The memory write cycle is begun when MRQ (Memory ReQuest) goes active out of the Z80. U46 (12,13,11) gates MRQ with RFSH so that GATED MRQ is only active during non-refresh cycles. Since the refreshing is handled by software reads, the Z80 hardware refresh cycle is ignored. GATED MRQ becomes the RAS (Row Address Select) for the DRAMS. That means that the row addresses are latched in to the RAM chips. The three multiplexers (U35-37) are sending the low 9 address bits through to the DRAM'S at this time.

Also, note that GATED MRQ is combined with RD in such a way that the DRAM WE (Write Enable) becomes active at the same time as MRQ. This allows data to be written into the memory.

GATED MRQ also goes to the D input of flip-flop U44. This causes MUX to go active (low) on the next rising edge of the Z8O clock, in order to provide the required delay between RAS being applied to the DRAMS and the multiplexers switch to the column addresses, which is controlled by MUX.

So far, we have the row address bits latched in to the DRAMS, and we've just switched the multiplexers so that the column data is presented to the address inputs. All that remains is to latch the column data in.

That happens when DMUX (Delayed MUX) goes active and enables U34 to output the appropriate CAS signal. DMUX is gated with A15 to ensure that the Z80 is calling upon the DRAM's and not the EPROM memory. Remember that A15 must be high to allow access of the DRAM memory. Notice that DMUX does not become active until after the column addresses are presented to the memory chips, since DMUX is actually an output from one of the multiplexers (U37). Proper delay time is ensured by the CAS signal only being generated after two additional gate delays caused by U46 (9,10,8) an U34.

U38 is a buffer to provide drive to the DRAM bank. The multiplexers (U35-37) are also buffers. The resistors help to control ringing and overshoot.

As your reward for reading through that discussion on the DRAM circuits, we'll now address the line answering section. It's much easier! The NE2 neon bulb couples the AC ring voltage thru to the opto-isolator (U56). R46 is the current limiting resistor, and D19 prevents U56 from being blown-out from reverse potentials. When a ring comes in, the opto-isolator turns on and the INT signal goes low. INT goes right to the Z80.

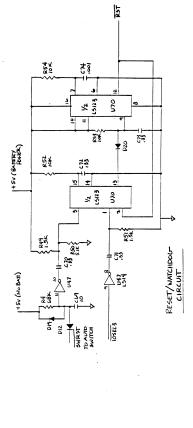

The watchdog timer and reset circuit (separate schematic) is made from U70, a dual timer IC, along with the associated components. The software makes sure that IOSEL3 is regularly pulsed low. If this signal stops doing this, the watchdog timer resets the Z80 since it is no longer properly running the program. C71 is a differentiator to ensure that the watchdog only responds to the edge of the pulses. If this were not incorporated, a problem which caused IOSEL3 to be continuously low would not be detected.

When the IOSEL3 signal stops, the first half of U70 times out and causes the second U70 half to output a reset pulse. This output is also fed back to the first timer to force continuous resets until the system starts up. The circuit associated with U47 (11,10) causes a reset upon power-up. Note that this circuit forces a reset upon re-application of AC power even when the battery is turned-on. All of this happens fast enough that the DRAM bank never loses data. In the event that a manual reset is ever needed, the AUTO button is wired to force a reset. The front panel LED count display is generated by the 1CM7217, a full counter display controller. It takes the count input from the U41 IO port, and the counter reset from the STOP button.

Circuit Description and Troubleshooting Audio circuit discussion

The audio circuitry is straightforward. The mic input is accepted as balanced by U60 (6,5,7). The line input is padded and applied in parallel with the mic input.

U60 (9,10,8) provides pre-emphasis.

U62 is the VCA (Voltage Controlled Amplifier), which performs the AGC action. D17, 18 rectify the audio to produce the control voltage. C14 is the time-constant capacitor. Attack and release times are controlled by R23 and R24.

A gating function is provided to freeze the gain when there is no audio input. This allows fairly aggressive processing without excessive artifacts (where have we heard that before?). The gating approach is unique. The amplified input audio is sent to both fast and slow rectifier/time constant networks (D14, 15 and associated parts), and the two resulting outputs are compared in an op-amp stage configured as a comparator, U61 (5,6,7). This accomplishes a "floating gate" function, which is relatively insensitive to input level. Thus, no gating threshold control is required, and superior gating action is obtained.

U63 (9,6,8) disconnects C14 when gating is active, thus freezing gain.

U63 (2,1,13 & 10,12,11) are used for meter switching. Either the play or record signals are routed to U61 (8,9,10) for amplification and the following parts, which provide the meter time constant, and on to the bar graph front panel meter module.

U57 is the CODEC IC, discussed earlier, which converts the audio to digital and back again. A balanced output from this IC is sent to the phone line transformer, and one side goes also to the speaker amplifier.

The audio drive to the speaker is provided by U59, a single-IC amplifier.

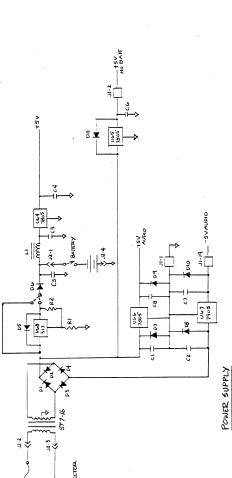

Circuit Description and Troubleshooting Power Supply

The power supply generates four outputs: +5 v logic (battery- backed), +5 v logic (no-battery), ÷5 v audio, and -5 v audio.

All but the 5 v battery-backed are simple three-leg regulator circuits. The battery-backed supply parallels the output from the rectifier with the battery. If AC goes away, the battery maintains power. Li prevents line spikes from getting through to the regulator and ultimately the logic and processor circuits.

Since the Echo is designed to be used for long periods of time unattended, a number of steps were taken to ensure proper operation even in the presence of AC power glitches.

- The AC connector is filtered.

- A split-type power transformer is used to reduce inter-winding capacitance.

- The battery prevents sags and momentary drops from causing problems.

- The coil (Li) reduces problems from line spikes.

- A large number of carefully chosen bypass capacitors are placed throughout the PC board.

- The watchdog timer immediately restarts the Z80 if it should stop running properly for any reason.

Voltage regulator U68 and its associated components are not used in some units, depending on battery type.

| Telos Systems ECHO VOICE STORAGE/RETRIEVAL SYSTEM |

|---------------------------------------------------|

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

| (This page intentionally left blank)              |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

Appendix

Timing Charts Manufacturers Data Sheets

FEBRUARY 1985

### SEMICONDUCTOR

## **MSM41256AS/RS** 262144-BIT DYNAMIC RANDOM ACCESS MEMORY -PAGE MODE

#### **GENERAL DESCRIPTION**

The OKI MSM41256 is a fully decoded, dynamic NMOS random access memory organized as 262144 one-bit words. The design is optimized for high-speed, high performance applications such as mainframe memory, buffer memory, peripheral storage and environments where low power dissipation and compact layout is required.

Multiplexed row and column address inputs permit the MSM41256 to be housed in a standard 16 pin DIP. Pin-outs conform to the JEDEC approved pin out.

The MSM41256 is fabricated using silicon gate NMOS and OKI's advanced Double-Layer Polysilicon process. This process, coupled with single-transistor memory storage calls, permits maximum circuit density and minimal chip size. Dynamic circuitry is employed in the design, including the sense amplifiers.

Clock timing requirements are noncritical, and power supply tolerance is very wide. All inputs and output are TTL compatible.

**BLOCK DIAGRAM**

#### **FEATURES**

- 262144 × 1 RAM, 16 pin peckage

- Silicon-gate, Double Poty NMOS, single transistor cell

Row access time,

- 150 ns max (MSM41258-15AS/RS)

- 200 ns mex (MSM41256-20AS/RS) Cycle time,

- 260 ns min (MSM41256-15AS/RS) 330 ns min (MSM41256-20AS/RS)

- Low power 385 mW active,

- 28 mW max standby

- Single +5V Supply, ±10% tolerance

All inputs TTL compatible, low capacitive load

- Three-state TTL compatible output

- "Gated" CAS

- 4 ms/256 refresh cycle

- Common I/O capability using "Early Write" operation

Output unlatched at cycle and allows extended page bounds.

- and two-dimensional chip select Read-Modify-Write, RAS-only refresh, and Page Mode

- On-chip latches for Addresses and Data-in

- On-chip substrate bias generator for high performance

#### PIN CONFIGURATION

| Pin Names                          | Function                 |

|------------------------------------|--------------------------|

| A <sub>0</sub> ~ A <sub>8</sub>    | Address Inputs           |

| RAS                                | Row Address<br>Strobe    |

| CAS                                | Column Address<br>Strobe |

| WE                                 | Write Enable             |

| Din                                | Data Input               |

| Dout                               | Data Output              |

| VCC                                | Power (+5V)              |

| V <sub>CC</sub><br>V <sub>SS</sub> | Ground (0V)              |

<sup>\*</sup> Refresh Address

### **ABSOLUTE MAXIMUM RATINGS**

$(Ta = 25^{\circ}C)$

| Rating                                                        | Symbol           | Value       | Unit |

|---------------------------------------------------------------|------------------|-------------|------|

| Voltage on any pin relative to V <sub>SS</sub>                | VIN, VOUT        | -1 to +7    | ٧    |

| Voltage on V <sub>CC</sub> supply relative to V <sub>SS</sub> | Vcc              | -1 to +7    | · V  |

| Operating temperature                                         | Topr             | 0 to 70     | °C   |

| Storage temperature                                           | T <sub>stg</sub> | -55 to +150 | °C   |

| Power dissipation                                             | PD               | 1.0         | W    |

| Short circuit output current                                  | los              | 50          | mA   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

(Referenced to V<sub>SS</sub>)

| Parameter                      | Symbol          | Min. | Тур. | Max. | Unit | Operating<br>Temperature |  |  |

|--------------------------------|-----------------|------|------|------|------|--------------------------|--|--|

| Supply Voltage                 | Vcc             | 4.5  | 5.0  | 5.5  | ٧    |                          |  |  |

|                                | V <sub>SS</sub> | 0    | 0    | 0    | ٧    | 200 1 700                |  |  |

| Input High Voltage, all inputs | ViH             | 2.4  |      | 6.5  | ٧    | 0°C to + 70°C            |  |  |

| Input Low Voltage, all inputs  | VIL             | -1.0 |      | 0.8  | ٧    |                          |  |  |

## DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                                | Symbol           | Min. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------|------------------|------|------|------|

| OPERATING CURRENT* Average power supply current (RAS, CAS cycling; t <sub>RC</sub> = min.)                               | I <sub>CC1</sub> |      | 75   | mA   |

| STANDBY CURRENT<br>Power supply current<br>(RAS = CAS = V <sub>IH</sub> )                                                | I <sub>CC2</sub> |      | 5.0  | mA   |

| REFRESH CURRENT<br>Average power supply current<br>(RAS cycling, CAS = V <sub>IH</sub> ; t <sub>RC</sub> = min.)         | I <sub>CC3</sub> |      | 60   | mĄ.  |

| PAGE MODE CURRENT* Average power supply current (RAS = V <sub>IL</sub> , CAS cycling; t <sub>PC</sub> = min.)            | <sup>l</sup> CC4 |      | 60   | mA   |

| INPUT LEAKAGE CURRENT Input leakage current, any input (OV ≤ V <sub>IN</sub> ≤ 6.5V, all other pins not under test = OV) | lu               | -10  | 10   | μА   |

| OUTPUT LEAKAGE CURRENT<br>(Data out is disabled,<br>OV   VOUT   5.5V)                                                    | lLO              | -10  | 10   | μΑ   |

| OUTPUT LEVELS Output high voltage (I <sub>OH</sub> = -5 mA) Output low voltage (I <sub>OL</sub> = 4.2 mA)                | V <sub>OH</sub>  | 2.4  | 0.4  | v    |

<sup>\*</sup>Note: ICC is dependent on output loading and cycle rates. Specified values are obtained with the output open.

#### **CAPACITANCE**

(T<sub>a</sub> = 25°C, f = 1 MHz)

| Parameter                                                              | Symbol           | Max. | Unit |

|------------------------------------------------------------------------|------------------|------|------|

| Input Capacitance (A <sub>0</sub> ~ A <sub>8</sub> , D <sub>IN</sub> ) | C <sub>IN1</sub> | 6    | pF   |

| Input Capacitance (RAS, CAS, WE)                                       | C <sub>IN2</sub> | 7    | pF   |

| Output Capacitance (DOUT)                                              | COUT             | 7    | pF   |

Note: Capacitance measured with Boonton Meter.

# AC CHARACTERISTICS Symbol Units MSM41256-15 MSM41256-20

| Desamates                                  | Cumbal           | l laite | MSM41256-15 |        | MSM41256-20 |        | Note |  |

|--------------------------------------------|------------------|---------|-------------|--------|-------------|--------|------|--|

| Parameter                                  | Symbol           | Units   | Min.        | Max.   | Min.        | Max.   | Note |  |

| Refresh period                             | †REF             | ms      |             | 4      |             | 4      |      |  |

| Random read or write cycle time            | <sup>t</sup> RC  | ns      | 260         |        | 330         |        |      |  |

| Read-write cycle time                      | <sup>t</sup> RWC | ns      | 325         |        | 410         |        |      |  |

| Page mode cycle time                       | <sup>t</sup> PC  | ns      | 145         |        | 190         |        |      |  |

| Access time from RAS                       | †RAC             | ns      |             | 150    |             | 200    | 4, 6 |  |

| Access time from CAS                       | †CAC             | ns      |             | 75     |             | 100    | 5, 6 |  |

| Output buffer turn-off delay               | <sup>t</sup> OFF | ns      | 0           | 40     | 0           | 50     |      |  |

| Transition time                            | t <sub>T</sub>   | ns      | 3           | 50     | 3           | 50     |      |  |

| RAS precharge time                         | <sup>t</sup> RP  | ns      | 100         |        | 120         |        |      |  |

| RAS pulse width                            | †RAS             | ns      | 150         | 10,000 | 200         | 10,000 |      |  |

| RAS hold time                              | <sup>t</sup> RSH | ns      | 75          |        | 100         |        |      |  |

| CAS precharge time                         | tCP              | ns      | 60          |        | 80          |        |      |  |

| CAS pulse width                            | <sup>t</sup> CAS | ns      | 75          | 10,000 | 100         | 10,000 |      |  |

| CAS hold time                              | t <sub>CSH</sub> | ns      | 150         |        | 200         |        |      |  |

| RAS to CAS delay time                      | <sup>t</sup> RCD | ns      | 25          | 75     | 30          | 100    | 7    |  |

| CAS to RAS precharge time                  | tCRP             | ns      | 0           |        | 0           |        |      |  |

| Row Address set-up time                    | †ASR             | ns      | 0           |        | 0           |        |      |  |

| Row Address hold time                      | <sup>t</sup> RAH | ns      | 20          |        | 25          |        |      |  |

| Column Address set-up time                 | tASC             | ns      | 0           |        | 0           |        |      |  |

| Column Address hold time                   | t <sub>CAH</sub> | ns      | 45          |        | 55          |        |      |  |

| Column Address hold time referenced to RAS | t <sub>AR</sub>  | ns      | 120         |        | 155         |        |      |  |

| Read command set-up time                   | <sup>t</sup> RCS | ns      | 0           |        | 0           |        |      |  |

| Read command hold time                     | <sup>t</sup> RCH | ns      | 0           |        | 0           |        |      |  |

| Write command set-up time                  | twcs             | ns      | 0           |        | 0           |        | 8    |  |

| Write command hold time                    | twcH             | ns      | 45          |        | 55          |        |      |  |

| Write command hold time referenced to RAS  | twcn             | ns      | 120         | ·      | 155         |        |      |  |

| Write command pulse width                  | twp              | ns      | 45          |        | 55          |        |      |  |

| Write command to RAS lead time             | <sup>t</sup> RWL | ns      | 60          |        | 80          |        |      |  |

| Write command to CAS lead time             | tCWL             | ns      | 60          |        | 80          |        |      |  |

| Data-in set-up time                        | tos              | ns      | 0           |        | 0           |        |      |  |

| Data-in hold time                          | tDH              | ns      | 45          |        | 55          |        |      |  |

| Data-in hold time referenced to RAS        | <sup>t</sup> ohr | ns      | 120         |        | 155         |        |      |  |

| CAS to WE delay                            | tCWD             | ns      | 75          |        | 100         |        | 8    |  |

| RAS to WE delay                            | tRWD             | ns      | 150         |        | 200         |        | 8    |  |

| Read command hold time referenced to RAS   | terh             | ns      | 20          |        | 25          |        |      |  |

NOTES: 1) An initial pause of 100  $\mu s$  is required after power-up followed by any 8 RAS cycles (Examples: RAS only refresh) before proper device operation is achieved.

AC measurements assume t<sub>T</sub> = 5 ns.

3) VIH (Min.) and VIL (Max.) are reference levels for measuring timing of input signals. Also, transition times are

V<sub>|H|</sub> (Min.) and v<sub>|L|</sub> (max.) are v<sub>|L|</sub> measured between V<sub>|H|</sub> and V<sub>|L|</sub>.

Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max.).

If t<sub>RCD</sub> is greater than the maximum recommended value shown in this table, t<sub>RAC</sub> will increase by the amount that t<sub>RCD</sub> exceeds the values shown.

5) Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max.).

6) Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

Measured with a load circuit equivalent to 2 TTL loads and 100 pF

Operation within the t<sub>RCD</sub> (max.) limit insures that t<sub>RAC</sub> (max.) can be met. t<sub>RCD</sub> (max.) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max.) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

t<sub>WCS</sub>, t<sub>CWD</sub> and t<sub>RWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; if t<sub>WCS</sub> ≥ t<sub>WCD</sub> (min.), the cycle is an early write cycle and the data out prin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min.) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min.) the cycle is read-write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions is obtained the gendition of the data out. is satisfied the condition of the data out (at access time) is indeterminate.

#### DESCRIPTION

#### ADDRESS INPUTS:

A total of eighteen binary input address bits are required to decode any 1 of 262144 storage cell locations within the MSM41256. Nine row-address bits are established on the input pins  $(A_0 \sim A_8)$  and latched with the Row Address Strobe (RAS). The nine column-address bits are established on the input pins and latched with the Column Address Strobe (CAS). All input addresses must be stable on or before the falling edge of RAS. CAS is internally inhibited (or "gated") by RAS to permit triggering of CAS as soon as the Row Address Hold Time (t<sub>RAH</sub>) specification has been satisfied and the address inputs have been changed from row-addresses to column-addresses.

The read mode or write mode is selected with the WE input. A logic high (1) on WE dictates read mode; logic low (0) dictates write mode. Data input is disabled when read mode is selected.

#### DATA INPUT:

DATA is written into the MSM41256 during a write or read-write cycle. The last falling edge of WE or CAS is a strobe for the Data in (D<sub>IN</sub>) register. In a write cycle, if WE is brought low (write mode) before CAS, D<sub>IN</sub> is strobed by CAS, and the set-up and hold times are referenced to CAS. In a read-write cycle, WE will be delayed until  $\overline{CAS}$  has made its negative transition. Thus  $D_{|N}$  is strobed by  $\overline{WE}$ , and set-up and hold times are referenced to  $\overline{WE}$ .

#### DATA OUTPUT:

The output buffer is three-state TTL compatible with a fan-out of two standard TTL loads. Data-out is the same polarity as data-in. The output is in a high impedance state until CAS is brought low. In a read cycle, or read-write cycle, the output is valid after t<sub>RAC</sub> from transition of RAS when t<sub>RCD</sub> (max.) is satisfied, or after t<sub>CAC</sub> from transition of CAS when the transition occurs after t<sub>RCD</sub> (max.).

Data remain valid until CAS is returned to a high level. In a write cycle the identical sequence occurs, but data is not valid.

#### PAGE MODE:

Page-mode operation permits strobing the row-address into the MSM41256 while maintaining  $\overline{\text{RAS}}$  at a logic low (0) throughout all successive memory operations in which the row-address doesn't change. Thus the power dissipated by the negative going edge of RAS is saved. Further, access and cycle times are decreased because the time normally required to strobe a new row-address is eliminated.

#### REFRESH:

Refresh of the dynamic memory cells is accomplised by performing a memory cycle at each of the 256 row-addresses (A $_0\sim A_7$  at least every four milliseconds. During refresh, either  $V_{IL}$  or  $V_{IH}$  is permitted for  $A_8$ .  $\overline{AAS}$  only refresh avoids any output during refresh because the output buffer is in the high impedance state unless  $\overline{CAS}$  is brought low. Strobing each of 256 row-addresses with  $\overline{AAS}$  will cause all bits in each row to be refreshed. Further RAS-only refresh results in a substantial reduction in power dissipation.

#### HIDDEN REFRESH:

RAS ONLY REFRESH CYCLE may take place while maintaining valid output data. This feature is referred to as Hidden Refresh. Hidden Refresh is performed by holding CAS as VIL from a previous memory read cycle.

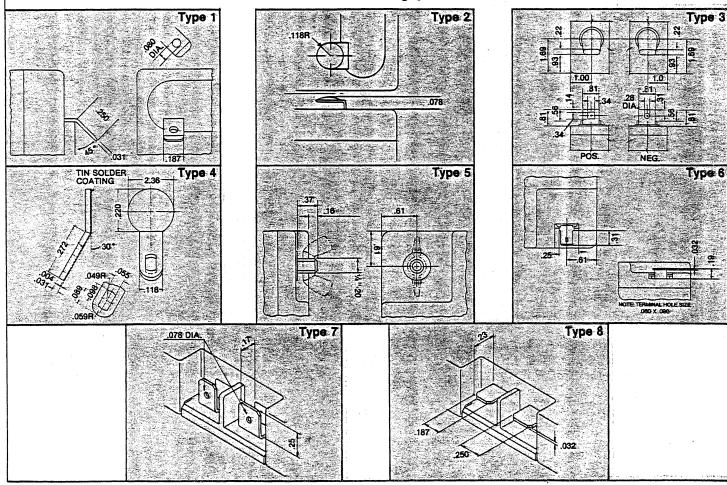

### **ORDERING INFORMATION**

| Speed    | Package<br>(Note 1) | Pins | Part Number     |

|----------|---------------------|------|-----------------|

|          | CDIP                |      | MSM 41256-15 AS |

| 150 nsec | 150 nsec PDIP 16    | 16   | MSM 41256-15 RS |

|          | CDIP                |      | MSM 41256-20 AS |

| 200 nsec | PDIP                | 16   | MSM 41256-20 RS |

Notes: PDIP = Molded dip CDIP = Ceramic side-brazed dip

|  | • |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  | • |  |

|  |   |  |

Telos Systems

Order Number 210629-002

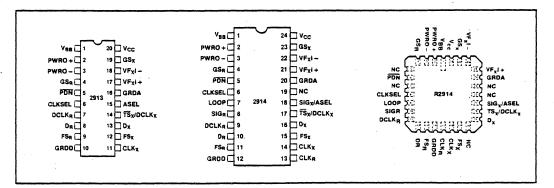

# 2913 AND 2914 COMBINED SINGLE-CHIP PCM CODEC AND FILTER

- 2914 Asynchronous clocks, 8th bit signaling, loop back test capability

- 2913 Synchronous clocks only, 300 mil package

- AT&T D3/D4 and CCITT Compatible

- Pin Selectable µ-law or A-law Operation

- Two Timing Modes:

- -Fixed Data Rate Mode 1.536, 1.544, or 2.048 MHz

- -- Variable Data Rate Mode 64 kHz-4.096 MHz

- Exceptional Analog Performance

- Low Power HMOS-E Technology:

- -5mW Typical Power Down

- -140mW Typical Operating

- Fully Differential Architecture Enhances

Noise Immunity

- On-Chip Auto Zero, Sample and Hold, and Precision Voltage References

- Direct Interface with Transformer or Electronic Hybrids

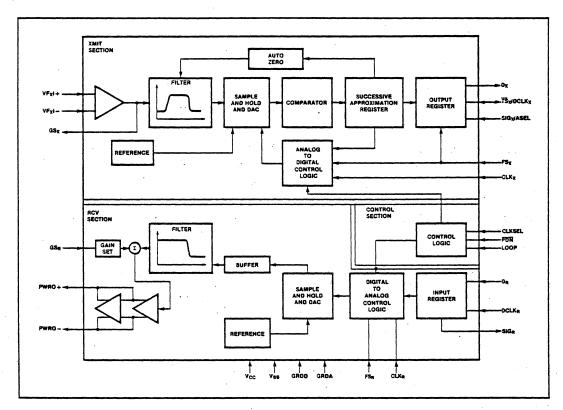

The Intel 2913 and 2914 are fully integrated PCM codecs with transmit/receive filters fabricated in a highly reliable and proven N-channel HMOS silicon gate technology. These devices provide the functions that were formerly provided by two complex chips (2910A or 2911A and 2912A). Besides the higher level of integration, the performance of the 2913 and 2914 is superior to that of the separate devices.

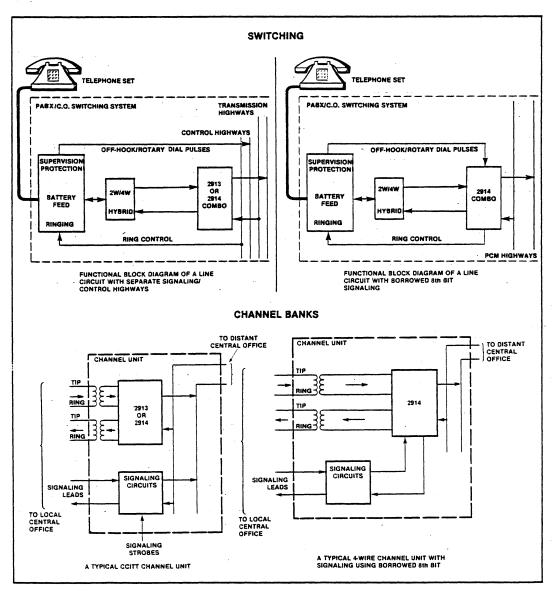

The primary applications for the 2913 and 2914 are in telephone systems:

- Switching—Digital PBX's and Central Office Switching Systems

- Transmission—D3/D4 Type Channel Banks and Subscriber Carrier Systems

- Subscriber Instruments—Digital Handsets and Office Workstations

The wide dynamic range of the 2913 and 2914 (78 dB) and the minimal conversion time make them ideal products for other applications such as:

- Voice Store and Forward

- Secure Communications Systems

- Digital Echo Cancellers

- · Satellite Earth Stations

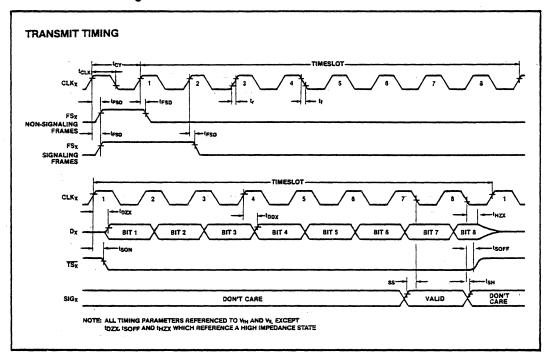

Figure 1. Pin Configurations

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licences are implied. Information Contained Herein Supercedes Previously Published Specifications On These Devices From Intel.

\*\*INTEL CORPORATION, 1983\*\*

September 1983

Figure 2 Block Diagram

Table 1. Pin Names

| V <sub>98</sub> | Power (-5V)                            | GS <sub>x</sub>     | Transmit Gain Control                |

|-----------------|----------------------------------------|---------------------|--------------------------------------|

| PWRO+, PWRO-    | Power Amplifier Outputs                | VFxI-, VFxI+        | Analog Inputs                        |

| GS <sub>R</sub> | Receive Gain Control                   | GRDA                | Analog Ground                        |

| PDN             | Power Down Select                      | NC                  | No Connect                           |

| CLKSEL          | Master Clock Frequency<br>Select       | SIG <sub>x</sub>    | Transmit Signaling Input             |

| LOOP            | Analog Loop Back                       | ASEL                | μ- or A-law Select                   |

| SIGR            | Receive Signaling Bit Output           | $\overline{TS}_{x}$ | Timeslot Strobe/Buffer Enable        |

| DCLKR           | Receive Variable Data Clock            | DCLK <sub>x</sub>   | Transmit Variable Data Clock         |

| D <sup>B</sup>  | Receive PCM Input                      | D <sub>x</sub>      | Transmit PCM Output                  |

| FS <sub>R</sub> | Receive Frame<br>Synchronization Clock | FS <sub>x</sub>     | Transmit Frame Synchronization Clock |

| GRDD            | Digital Ground                         | CLKx                | Transmit Master Clock                |

| V <sub>cc</sub> | Power (+5V)                            | CLK                 | Receive Master Clock                 |

Table 2, Pin Description

| Symbol            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>BB</sub>   | Most negative supply; input voltage is -5 volts ±5%.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PWRO+             | Non-inverting output of power amplifier. Can drive transformer hybrids or high impedance loads directly in either a differential or single ended configuration.                                                                                                                                                                                                                                                                                                                        |

| PWRO-             | Inverting output of power amplifier. Functionally identical and complementary to PWRO+.                                                                                                                                                                                                                                                                                                                                                                                                |

| GS <sub>R</sub>   | Input to the gain setting network on the output power amplifier. Transmission level can be adjusted over a 12dB range depending on the voltage at GS <sub>R</sub> .                                                                                                                                                                                                                                                                                                                    |

| PDN               | Power down select. When PDN is TTL high, the device is active. When low, the device is powered down.                                                                                                                                                                                                                                                                                                                                                                                   |

| CLKSEL            | Input which must be pinstrapped to reflect the master clock frequency at CLK <sub>X</sub> , CLK <sub>B</sub> .  CLKSEL = V <sub>BB</sub> 2.048 MHz  CLKSEL = GRDD 1.544 MHz  CLKSEL = V <sub>CC</sub> 1.536 MHz                                                                                                                                                                                                                                                                        |

| LOOP              | Analog loopback. When this pin is TTL high, the analog output (PWRO+) is internally connected to the analog input (VF $_X$ l+), GS $_R$ is internally connected to PWRO-, and VF $_X$ l- is internally connected to GS $_X$ . A 0dBm0 digital signal input at D $_R$ is returned as a +3dBm0 digital signal output at D $_X$ .                                                                                                                                                         |

| SIG <sub>R</sub>  | Signaling bit output, receive channel. In fixed data rate mode, SIG <sub>R</sub> outputs the logical state of the eighth bit of the PCM word in the most recent signaling frame.                                                                                                                                                                                                                                                                                                       |

| DCLK <sub>R</sub> | Selects the fixed or variable data rate mode. When DCLK <sub>R</sub> is connected to V <sub>BB</sub> , the fixed data rate mode is selected. In this mode, the device is fully compatible with intel 2910A and 2911A direct mode timing. When DCLK <sub>R</sub> is not connected to V <sub>BB</sub> , the device operates in the variable data rate mode. In this mode DCLK <sub>R</sub> becomes the receive data clock which operates at TTL levels from 64kB to 4.096 MB data rates. |

| D <sub>R</sub>    | Receive PCM input. PCM data is clocked in on this lead on eight consecutive negative transitions of the receive data clock; CLK <sub>R</sub> in the fixed data rate mode and DCLK <sub>R</sub> in variable data rate mode.                                                                                                                                                                                                                                                             |

| FSR               | 8KHz frame synchronization clock input/ timeslot enable, receive channel. A multifunction input which in fixed data rate mode distinguishes between signaling and non-signaling frames by means of a double or single wide pulse respectively. In variable data rate mode this signal must remain high for the entire length of the timeslot. The receive channel enters the standby state whenever FS <sub>R</sub> is TTL low for 300 milliseconds.                                   |

| scription                          |                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                             | Function                                                                                                                                                                                                                                                                                                                                                                                           |

| GRDD                               | Digital ground for all internal logic circuits.  Not internally tied to GRDA.                                                                                                                                                                                                                                                                                                                      |

| CLKR                               | Receive master and data clock for the fixed data rate mode; receive master clock only in variable data rate mode.                                                                                                                                                                                                                                                                                  |

| CLK <sub>X</sub>                   | Transmit master and data clock for the fixed data rate mode; transmit master clock only in variable data rate mode.                                                                                                                                                                                                                                                                                |

| FS <sub>X</sub>                    | 8 KHz frame synchronization clock input/timeslot enable, transmit channel. Operates independently but in an analogous manner to FS <sub>R</sub> . The transmit channel enters the standby state whenever FS <sub>X</sub> is TTL low for 300 milliseconds.                                                                                                                                          |

| D <sub>X</sub>                     | Transmit PCM output. PCM data is clocked out on this lead on eight consecutive positive transitions of the transmit data clock: CLK <sub>X</sub> in fixed data rate mode and DCLK <sub>X</sub> in variable data rate mode.                                                                                                                                                                         |

| TS <sub>X</sub> /DCLK <sub>X</sub> | Transmit channel timeslot strobe (output) or data clock (input) for the transmit channel. In fixed data rate mode, this pin is an open drain output designed to be used as an enable signal for a three-state buffer as in 2910A and 2911A direct mode timing. In variable data rate mode, this pin becomes the transmit data clock which operates at TTL levels from 64kB to 4.096 MB data rates. |

| SIG <sub>X</sub> /ASEL             | A dual purpose pin. When connected to $V_{BB}$ , A-law operation is selected. When it is not connected to $V_{BB}$ this pin is a TTL level input for signaling operation. This input is transmitted as the eighth bit of the PCM word during signaling frames on the $D_X$ lead.                                                                                                                   |

| NC                                 | No connect                                                                                                                                                                                                                                                                                                                                                                                         |

| GRDA                               | Analog ground return for all internal voice circuits. Not internally connected to GRDD.                                                                                                                                                                                                                                                                                                            |

| VF <sub>X</sub> I+                 | Non-inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                          |

| VF <sub>X</sub> I-                 | Inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                              |

| GS <sub>X</sub>                    | Output terminal of on-chip uncommitted op amp. Internally, this is the voice signal input to the transmit filter.                                                                                                                                                                                                                                                                                  |

| Vcc                                | Most positive supply; input voltage is +5 volts ±5%.                                                                                                                                                                                                                                                                                                                                               |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **FUNCTIONAL DESCRIPTION**

The 2913 and 2914 provide the analog-to-digital and the digital-to-analog conversions and the transmit and receive filtering necessary to interface a full duplex (4 wires) voice telephone circuit with the PCM highways of a time division multiplexed (TDM) system. They are intended to be used at the analog termination of a PCM line or trunk.

The following major functions are provided:

- Bandpass filtering of the analog signals prior to encoding and after decoding

- Encoding and decoding of voice and call progress information

- Encoding and decoding of the signaling and supervision information

Figure 3. Typical Line Terminations

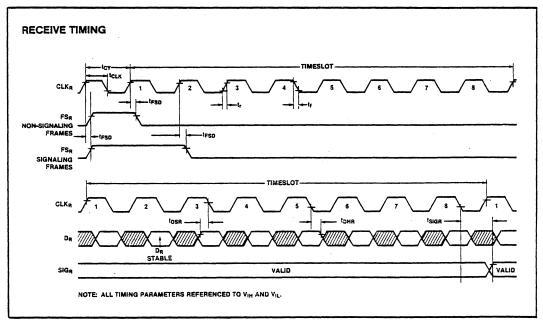

#### **WAVEFORMS**

#### **Fixed Data Rate Timing**

#### TRANSMIT SECTION, VARIABLE DATA RATE MODE1

| Symbol           | Parameter                             | Min | Тур | Max               | Unit | Test Conditions                |

|------------------|---------------------------------------|-----|-----|-------------------|------|--------------------------------|

| trsox            | Timeslot Delay from DCLK <sub>X</sub> | -80 |     | 80                | ns   |                                |

| t <sub>FSD</sub> | Frame Sync Delay                      | 0   |     | 120               | ns   |                                |

| toox             | Data Delay from DCLK <sub>X</sub>     | 0   |     | 100               | ns   | 0 < C <sub>LOAD</sub> < 100 pf |

| toon             | Timeslot to D <sub>X</sub> Active     | 0   |     | 50                | ns   | 0 < C <sub>LOAD</sub> < 100 pf |

| tooff            | Timeslot to D <sub>X</sub> Inactive   | 0   |     | 80                | ns   | 0 < C <sub>LOAD</sub> < 100 pf |

| fox              | Data Clock Frequency                  | 64  |     | 2048 <sup>2</sup> | kHz  | ·                              |

| torsx            | Data Delay from FS <sub>x</sub>       | - 0 |     | 140               | ns   | t <sub>TSOX</sub> = 80 ns      |

#### RECEIVE SECTION, VARIABLE DATA RATE MODE

| Symbol            | Parameter                             | Min | Тур | Max               | Unit | Test Conditions |

|-------------------|---------------------------------------|-----|-----|-------------------|------|-----------------|

| t <sub>TSDR</sub> | Timeslot Delay from DCLK <sub>R</sub> | -80 |     | 80                | ns   |                 |

| t <sub>FSD</sub>  | Frame Sync Delay                      | 0   |     | 120               | ns   | ·               |

| tosa              | Data Setup Time                       | 10  |     |                   | ns   |                 |

| t <sub>OHR</sub>  | Data Hold Time                        | 60  |     |                   | ns   |                 |

| for .             | Data Clock Frequency                  | 64  |     | 2048 <sup>2</sup> | kHz  |                 |

| tsen              | Timeslot End Receive Time             | 0   |     |                   | ns   | -               |

#### 64 KB OPERATION, VARIABLE DATA RATE MODE

| Symbol            | Parameter                            | Min  | Тур | Max | Unit | Test Conditions                                    |

|-------------------|--------------------------------------|------|-----|-----|------|----------------------------------------------------|

| teslx             | Transmit Frame Sync Minimum Downtime | 488  |     |     | ns   | FS <sub>x</sub> is TTL high for remainder of frame |

| tesla             | Receive Frame Sync Minimum Downtime  | 1952 |     |     | ns   | FS <sub>R</sub> is TTL high for remainder of frame |

| † <sub>DCLK</sub> | Data Clock Pulse Width               |      |     | 10  | μs   |                                                    |

#### NOTES:

Timing parameters t<sub>OON</sub> and t<sub>DOFF</sub> are referenced to a high impedance state.

Devices are available which operate at data rates up to 4.096 MHz.

### 51C256L LOW POWER 256K X 1 CHMOS DYNAMIC RAM

|                                    | 51C256L-15 | 51C256L-20 |

|------------------------------------|------------|------------|

| Maximum Access Time (ns)           | 150        | 200        |

| Maximum CHMOS Standby Current (mA) | · 0.1      | 0.1        |

- Low Power Data Retention

- Standby current, CHMOS 100 μA (max.)

- Refresh period, RAS-Only 32 ms (max)

- Data Retention Current 230 μA (max.)

- Low Operating Current 65 mA (max.)

- TTL and HCT Compatible

- Low Input/Output Capacitance

- High Reliability Plastic 16 Pin DIP

Intel® 51C256L is a low power 262,144 X 1 dynamic Random Access Memory. Fabricated on Intel's CHMOS III-D technology, the 51C256L offers features not provided by an NMOS dynamic RAM: CHMOS standby current and extended RAS-Only refresh for low data retention power. All inputs and outputs are TTL and HCT compatible and the input and output capacitances are significantly lowered to allow increased system performance.

The 51C256L offers a maximum standby current of 100  $\mu$ A when  $\overline{RAS} > V_{DD} = 0.5V$ . During standby (i.e. refresh only cycles), the refresh period can be extended to 32 ms to reduce the total current required for data retention to less than 230  $\mu$ A (max). The 51C256L combines this low power with high density for portable and battery backup applications.

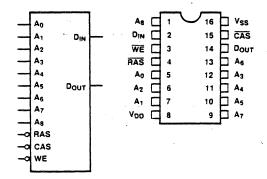

#### LOGIC SYMBOL PIN CONFIGURATION

#### **PIN NAMES**

| RAS                            | ROW ADDRESS STROBE    |

|--------------------------------|-----------------------|

| CAS                            | COLUMN ADDRESS STROBE |

| WE                             | WRITE ENABLE          |

| A <sub>0</sub> -A <sub>8</sub> | ADDRESS INPUTS        |

| DiN                            | DATA INPUT            |

| Dout                           | DATA OUTPUT           |

| V <sub>DD</sub>                | POWER (+5V)           |

| Vss                            | GROUND                |

|                                |                       |

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses are Implied. ©Intel Corporation, 1984

June, 1984

Order Number: 280031-001

#### **ABSOLUTE MAXIMUM RATINGS**†

| Ambient Temperature Under                                          |   |

|--------------------------------------------------------------------|---|

| Bias 10°C to +80°                                                  | C |

| Storage TemperaturePlastic -55°C to +125°                          | C |

| Voltage on Any Pin except V <sub>DD</sub> and D <sub>OUT</sub>     |   |

| Relative to V <sub>SS</sub>                                        | ١ |

| Voltage on V <sub>DD</sub> Relative to V <sub>SS</sub> 1.0V to 7.5 |   |

| Voltage on D <sub>OUT</sub>                                        |   |

| Relative to V <sub>SS</sub> 2.0V to V <sub>DD</sub> +1             | ٧ |

| Data Out Current50 m                                               | ۵ |

| Power Dissipation1.0\                                              | ٨ |

|                                                                    |   |

#### †COMMENT:

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. CHARACTERISTICS<sup>1</sup>

$T_A = 0$  °C to 70 °C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

|                   |                                                            |      | 51C256L | -                   |      |                                                                                                         |      |

|-------------------|------------------------------------------------------------|------|---------|---------------------|------|---------------------------------------------------------------------------------------------------------|------|

| Symbol            | Parameter                                                  | Min. | Typ.2   | Max.                | Unit | Test Conditions                                                                                         | Note |

| 1                 | V <sub>pp</sub> Supply Current,                            |      | 48      | 65                  | mA   | t <sub>RC</sub> = t <sub>RC</sub> (min), for - 15 specification                                         | 2.4  |

| 1001              | Operating                                                  |      | 35      | 50                  | mA   | t <sub>RC</sub> = t <sub>RC</sub> (min), for -20 specification                                          | 3.4  |

| I <sub>DD2</sub>  | V <sub>DD</sub> Supply Current,<br>TTL Standby             |      | 1       | 2                   | mA   | RAS and CAS at V <sub>IH</sub> , all other inputs and output ≥V <sub>SS</sub>                           |      |

| 1                 | V <sub>DD</sub> Supply Current,                            |      | 45      | 65                  | mA   | t <sub>RC</sub> = t <sub>RC</sub> (min), for -15 specification                                          | 1    |

| Горз              | RAS-only Refresh                                           |      | 35      | 50                  | mA   | $t_{RC} = t_{RC}$ (min), for -20 specification                                                          | 4    |

| l <sub>DD5</sub>  | V <sub>DD</sub> Supply Current.<br>Standby, Output Enabled |      | 3       | 4                   | mA   | RAS at V <sub>IH</sub> , CAS at V <sub>IL</sub> , all other inputs and output ≥ V <sub>SS</sub>         | 3    |

| loos              | V <sub>DD</sub> Supply Current,<br>CHMOS Standby           |      | 0.01    | 0.1                 | mA   | RAS ≥ V <sub>DD</sub> = 0.5V and CAS at V <sub>IH</sub> , all other inputs and output ≥ V <sub>SS</sub> |      |

| lu                | Input Load Current<br>(any pin)                            |      |         | 1                   | μА   | $V_{IN} = V_{SS}$ to $V_{DQ}$                                                                           |      |

| l <sub>lo</sub> , | Output Leakage Current for<br>High Impedance State         |      |         | 10                  | μА   | RAS and CAS at V <sub>IH</sub> ,<br>D <sub>OUT</sub> = V <sub>SS</sub> to V <sub>DD</sub>               |      |

| V <sub>IL</sub>   | Input Low Voltage<br>(all inputs)                          | -1.0 |         | 0.8                 | ٧    |                                                                                                         | 5    |

| V <sub>IH</sub>   | Input High Voltage<br>(all inputs)                         | 2.4  |         | V <sub>DO</sub> + 1 | ٧    |                                                                                                         | 5    |

| V-                | Output Low Voltage                                         |      |         | 0.4                 | ٧    | l <sub>OL</sub> = 4.2 mA                                                                                | 6    |